#### **Network on Metachip Architectures**

Ismo Hänninen\*, Wayne Buckhanan, Michael Niemier, Gary Bernstein Center for Nano Science and Technology

University of Notre Dame Notre Dame, IN 46556 +1-574-631-0996

ismo.hanninen@nd.edu \* And Tampere University of Technology, Finland

**Jason Kulick** Indiana Integrated Circuits, LLC 1400 E. Angela Blvd., Unit 107 South Bend, IN 46617 +1-574-217-4612 jason.kulick@indianaic.com

Network on Metachip Architectures, NoCArc 2012, December 1st

1

# Outline

- Introduction: Metachips & Quilt Packaging<sup>®</sup>

- Signal Performance

- Interconnections and Quilt Size

- Memory Access on a Quilt

- Quilted Multiprocessor SoC

- Conclusion

Introduction:

## **METACHIPS & QUILT PACKAGING®**

3 Network on Metachip Architectures, NoCArc 2012, December 1st

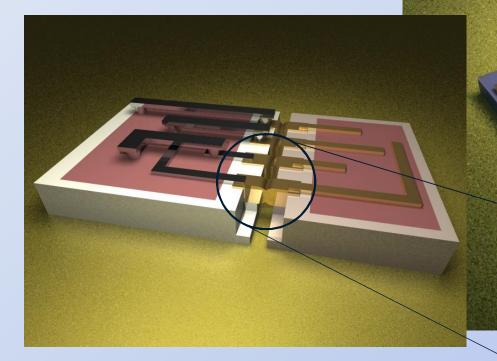

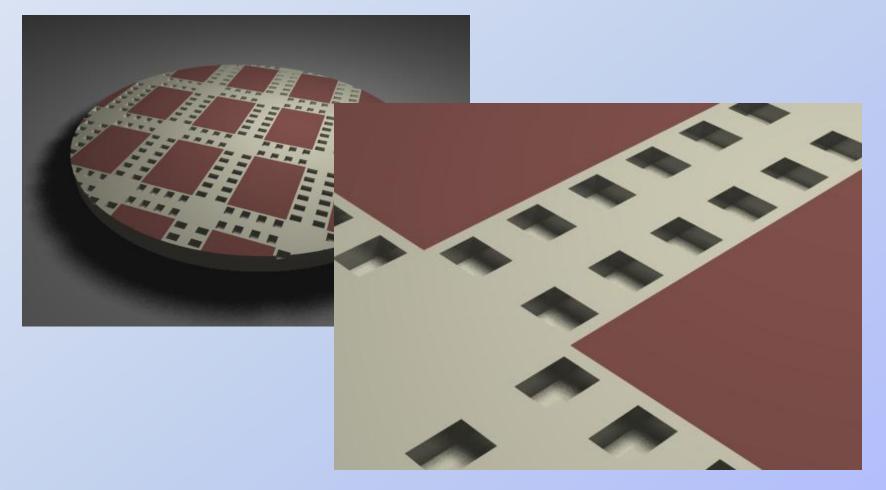

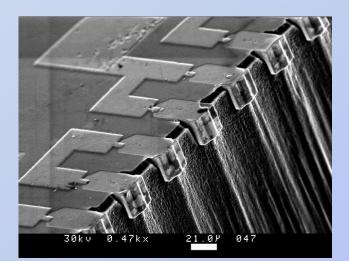

### **Quilt Packaging Process - General**

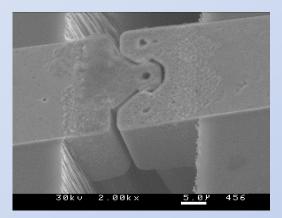

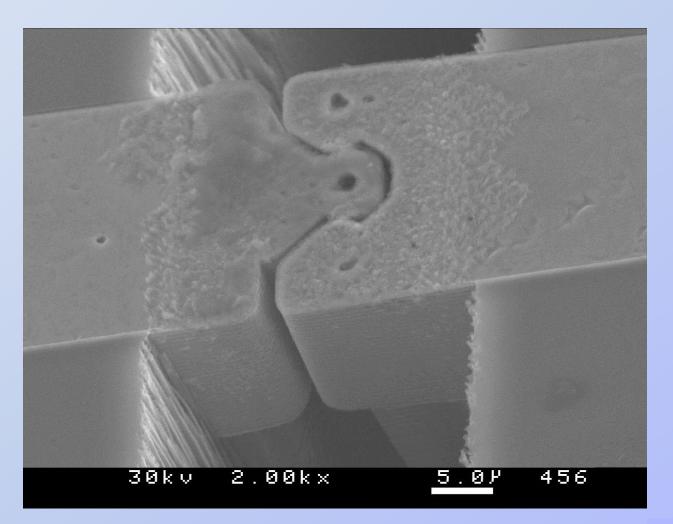

#### Bare die interconnect directly through edges

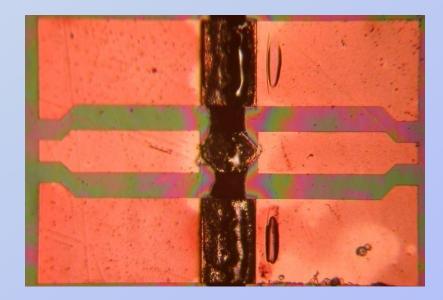

4 Network on Metachip Architectures, NoCArc 2012, December 1st **Cutaway view of nodules**

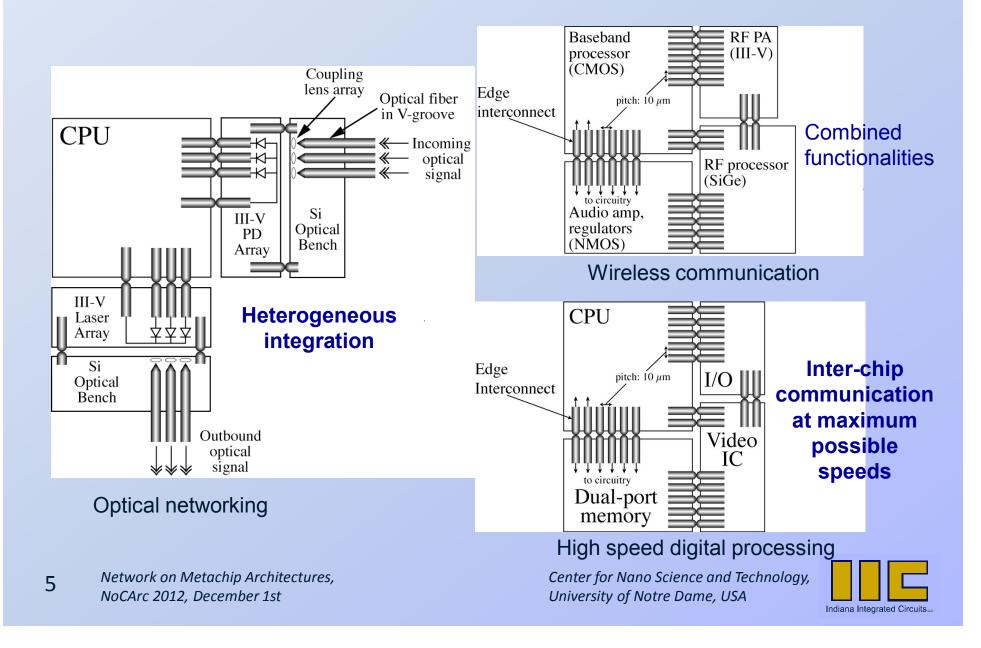

## Some Applications of Quilt Packaging

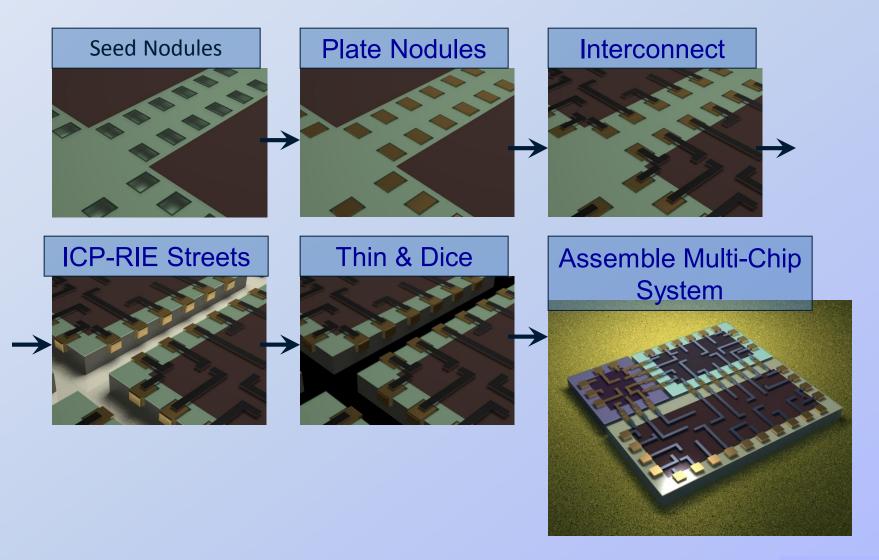

#### **Quilt Packaging Fabrication**

Etch Nodule Templates after IC front end fabrication

Network on Metachip Architectures, NoCArc 2012, December 1st

Center for Nano Science and Technology, University of Notre Dame, USA

6

#### **Quilt Packaging Fabrication**

Network on Metachip Architectures, NoCArc 2012, December 1st Center for Nano Science and Technology, University of Notre Dame, USA

7

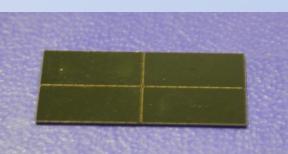

# Quilted Chips are Packaged as if Monolithic

Flip chip quilts also an option. Network on Metachip Architectures, 8

NoCArc 2012, December 1st

# Advantages of Quilt Packaging

- Heterogeneous integration of ICs and components fabricated using different processes (e.g. nanotechnology and CMOS)

- Better thermal control due to all chips on heat sink

- Simpler fabrication than chip stacking

- High signal bandwidth with excellent signal integrity

- Reduced power dissipation and die size (up to 50%) through reduction of pin I/O drivers and package capacitances

- Cost reduction by eliminating some packages and reducing package and board complexities

- Flexible use of IP and cores mix and match not large development cost for new "quilt"

- Decreased electrical noise

- Decreased need for passives

- Thinner profiles compared to chip stacking or PoP

- Variety of interconnect widths available simultaneously Can be used in combination with existing packaging strategies

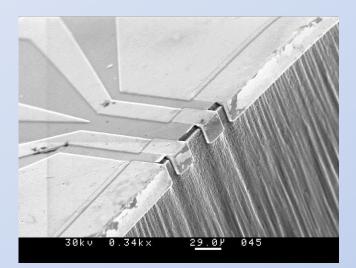

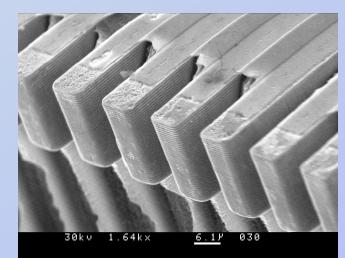

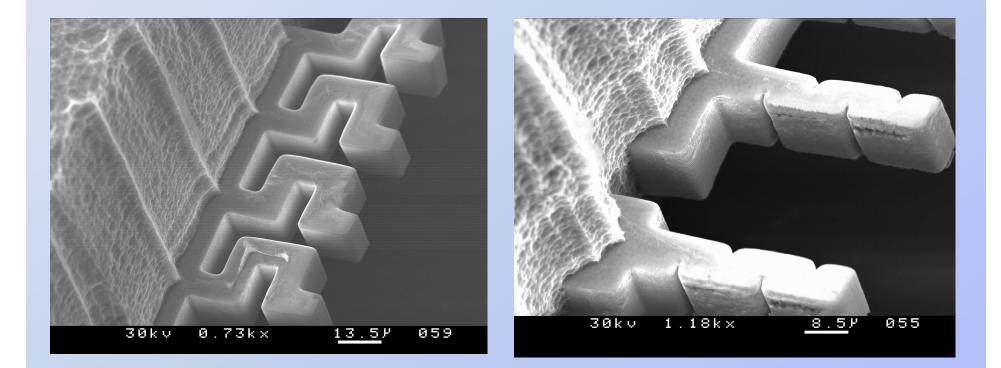

## Various Nodule Geometries to 10 µm

10 Network on Metachip Architectures, NoCArc 2012, December 1st

### 10- and 20-µm-wide Keyed Nodules

$10-\mu m$  wide,  $20-\mu m$  thick

10-mm chip would support 500 10- $\mu$ m wide nodules on one side.

#### 20-µm wide

Center for Nano Science and Technology, University of Notre Dame, USA

Interlocking

400 µm

Keys aid

fabricated

alignment

Degree of

protrusion,

key shape,

well controlled

nodules 10 µm to

Network on Metachip Architectures, 11 NoCArc 2012, December 1st

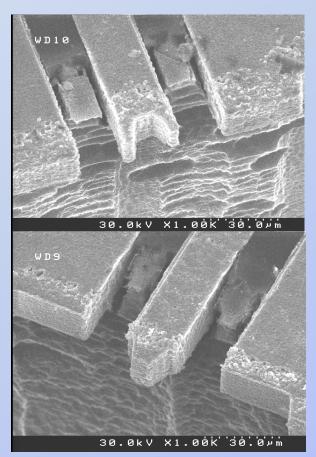

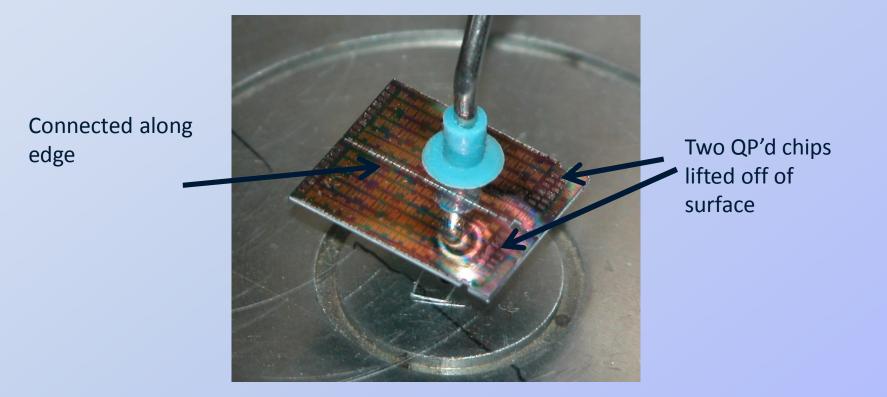

# Nodules are Physically Strong – Chip Supported by Edge Only

12 Network on Metachip Architectures, NoCArc 2012, December 1st

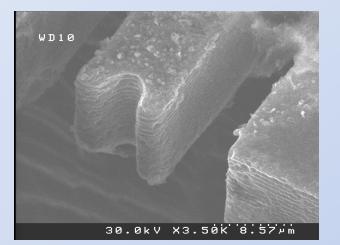

#### **Interlocking Nodules**

13 Network on Metachip Architectures, NoCArc 2012, December 1st

## **Compliant Nodules**

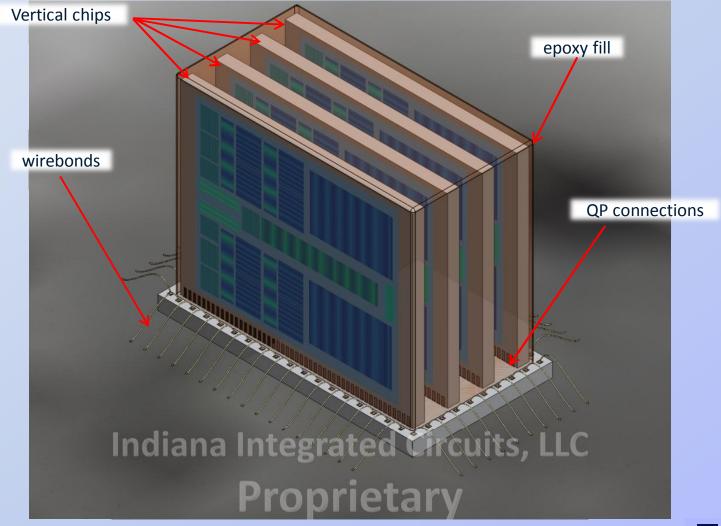

## 3D QP Concept

15 Network on Metachip Architectures, NoCArc 2012, December 1st

Measurements:

### **SIGNAL PERFORMANCE**

16 Network on Metachip Architectures, NoCArc 2012, December 1st

# Quilt Interconnect RF Performance

- Typical interconnect:

- 100  $\mu$ m nodule

- Tapered signal line, straight CPW ground lines

- 100 µm pitch GSG probe pads

- 8 kΩ-cm substrate resistivity

- 400 µm substrate thickness

- Cu interconnect, 1 μm Sn solder plating

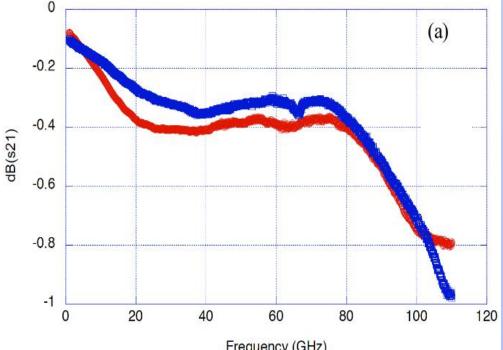

## **RF Performance: Insertion loss**

- S-parameters measured on-wafer, 10 MHz – 110 GHz

- Nodule and test pad insertion loss curves track §

- Loss attributable to nodules < 0.1dB to 110 GHz

- Loss including pads and launcher:

- < 0.4 dB below 80 GHz</p>

- <1 dB to 110 GHz</p>

Red: Nodules and test pads Blue: Test pads alone

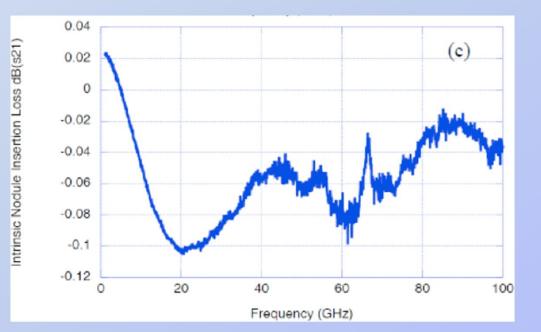

# Intrinsic QP RF Performance

- De-embedding effects of pads, launcher:

- Intrinsic QP nodule

loss < 0.1 dB to</li>

100 GHz

- Nearly flat lossvs. frequencycharacteristic

Promising for extremely wide bandwidth systems

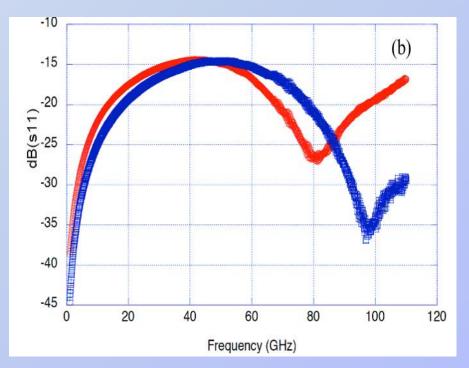

# **RF Performance: Return loss**

- Return loss shows a quarterwavelength resonance

- Unintended mismatch in the lines

- $Z_0$  is 59.8  $\Omega$ , nominal 50  $\Omega$ .

- Characteristic of high quality transmission lines

- QP resonance at lower frequency

- Consistent with increased transmission line length due to nodules

#### Red: Nodules and test pads Blue: Test pads alone

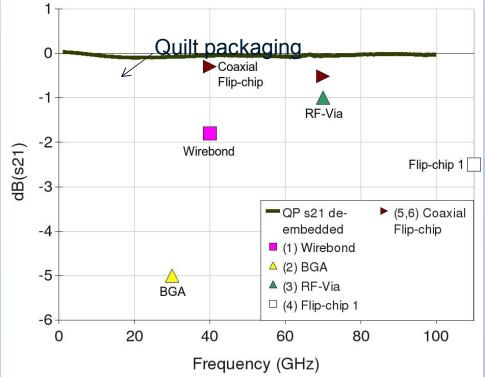

# **Comparison to Other Technologies**

- De-embedded insertion loss compared with recent papers on wirebonds, ball grid array, MS-to-CPW RF-via, flip chip.

- 0.25 dB lower than coaxial flip-chip via at 40GHz

- 1.7 dB lower than standard flip-chip at 110 GHz

- 0.8 dB lower than RF-via at 70 GHz

- 1. Sutano et al. IEEE Trans. Adv. Packaging, Vol 24, No. 4, Pg. 595. Nov. 2001.

- 2. Heyan, et. al. IEEE Trans. Microwave Theory and Tech., Vol. 51, No. 12, Pg. 2589. Dec 2003.

- 3. Hsu, et. al. CS-Mantech Conference, "Fabrication Process and 110GHz measurement result of MS-to-CPW RF-Via Transition for RF-MEMS Devices Packaging Applications" May 18-21 2009.

- 4. Cho, et. al. Microwave and Optical Technology Letters, Vol 51, No. 5, Pg. 1821. May 2009.

- 5. W. Wu, et al. IEEE Trans. Adv. Packaging, Vol 32, No. 2, Pg. 362, May 2009

- 6. W. Wu et al. IEEE Microwave and Component Letters, Vol. 17, No. 11, Nov. 2007

#### QP demonstrates a world record for lowloss chip-to-chip interconnect!

21 Network on Metachip Architectures, NoCArc 2012, December 1st

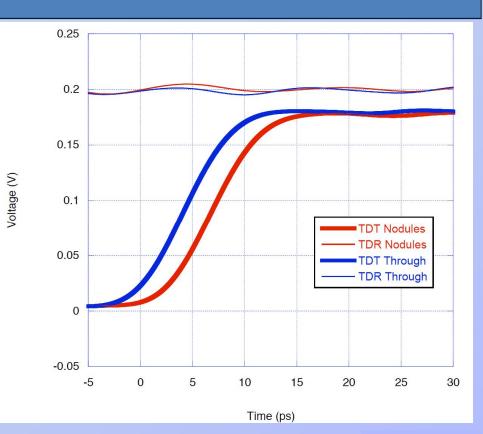

# **Time-Domain Performance**

- Single-ended GSG CPW configuration

- Picosecond Pulse Labs 4022 TDR pulse enhancement module:

9 ps risetime

- Total delay including probe pads, launcher: 7 ps (820 µm length)

- Delay due to QP nodules: 2.7 ps

100 µm nodule compared with pads/launcher, GSG

Center for Nano Science and Technology, University of Notre Dame, USA

22 Network on Metachip Architectures, NoCArc 2012, December 1st

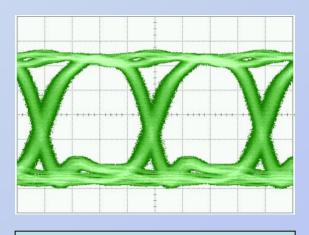

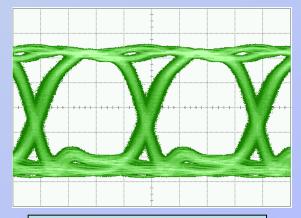

# Eye diagrams

- Measurement of 12 Gb/s eye pattern (Anritsu MP1763B)

- Horiz. 100 mV/div

- Vert. 20 ps/div

- Data stream: 2<sup>31</sup>-1 pseudorandom bit sequence

- Nearly ideal interconnect performance; indistinguishable from PG.

- Error-free operation

- SNR (Q) = 12.9 for pattern generator alone, 12.4 after chip-to-chip interconnect

#### Raw pattern generator

#### 50 µm GSG eye

What to expect of quilted metachips:

# INTERCONNECTIONS AND QUILT SIZE

24 Network on Metachip Architectures, NoCArc 2012, December 1st

# **Chip Interconnects**

50—200 homogeneous interconnection nodules per chip edge millimeter

| $\Rightarrow$ | thousands |

|---------------|-----------|

|               | of wires  |

|               | per chip  |

|               | edge      |

| Chip      | Nodule/gap width (μm) |      |      |

|-----------|-----------------------|------|------|

| edge (mm) | 2.5                   | 5    | 10   |

| 1.0       | 200                   | 100  | 50   |

| 2.0       | 400                   | 200  | 100  |

| 5.0       | 1000                  | 500  | 250  |

| 10.0      | 2000                  | 1000 | 500  |

| 20.0      | 4000                  | 2000 | 1000 |

| 40.0      | 8000                  | 4000 | 2000 |

• Various heterogeneous configurations possible

25 Network on Metachip Architectures, NoCArc 2012, December 1st

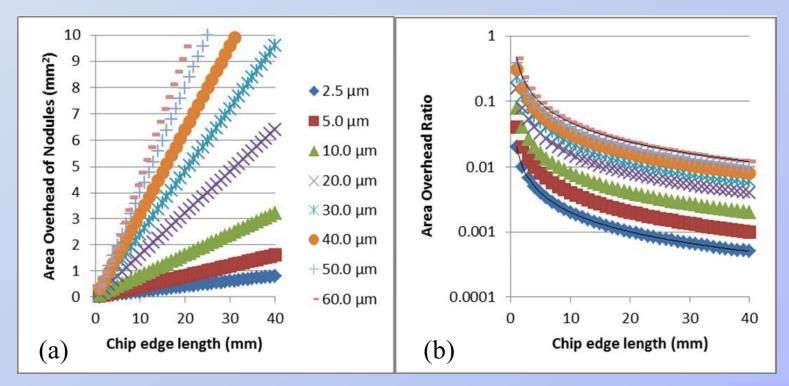

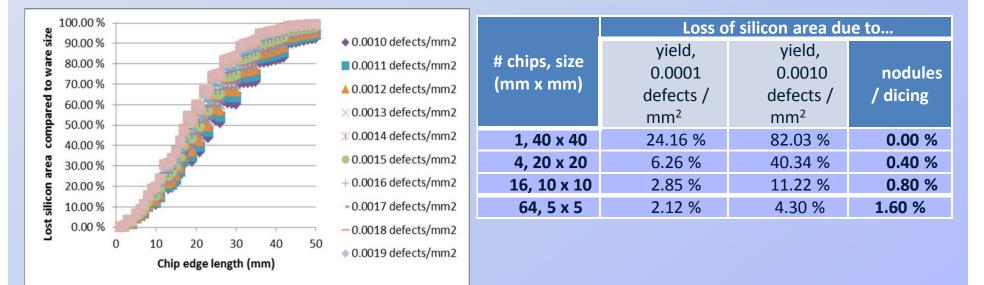

## Silicon Area and Yield...

Interconnection nodules consume very little silicon area, typically << 1 %</li>

# ...Silicon Area and Yield

• Chip size affects IC fabrication yield, especially on deep-submicron technologies

⇒ QP offers silicon savings with high yield

Removing the bottlenecks:

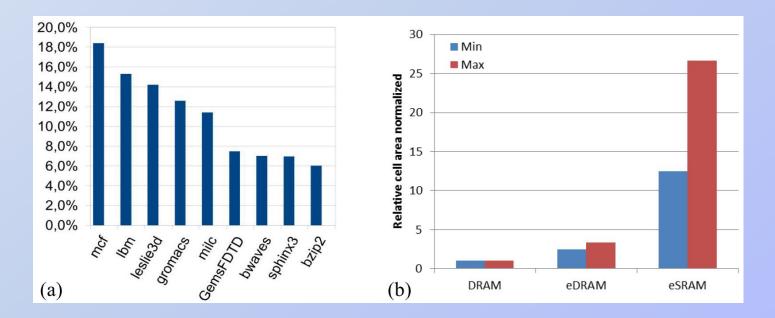

## **MEMORY ACCESS ON A QUILT**

28 Network on Metachip Architectures, NoCArc 2012, December 1st

# **Quilted SoC Memory**

- Quilted architecture alleviates memory system bottlenecks

- Reduced physical distance vs. external memory chip

- Improved memory density vs. single chip SoC

- Wide bus access!

29 Network on Metachip Architectures, NoCArc 2012, December 1st

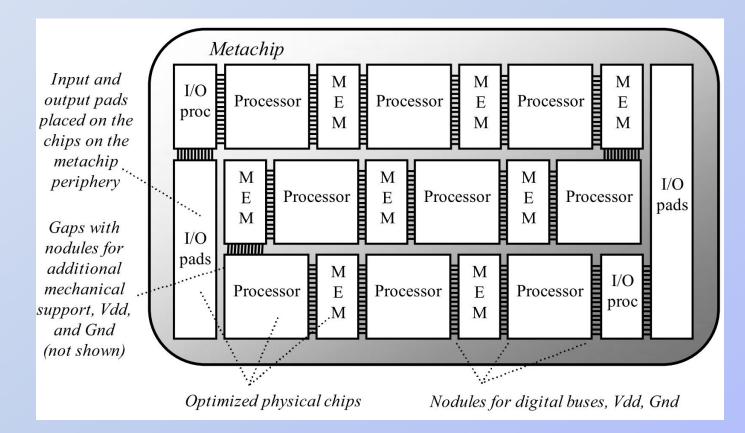

The dream:

## **QUILTED MULTIPROCESSOR SOC**

30 Network on Metachip Architectures, NoCArc 2012, December 1st

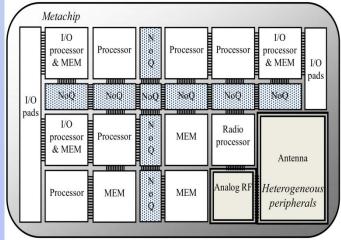

## **MPSoC** with Local Memories

System-on-a-Quilt (SoQ) for DSP applications

31 Network on Metachip Architectures, NoCArc 2012, December 1st

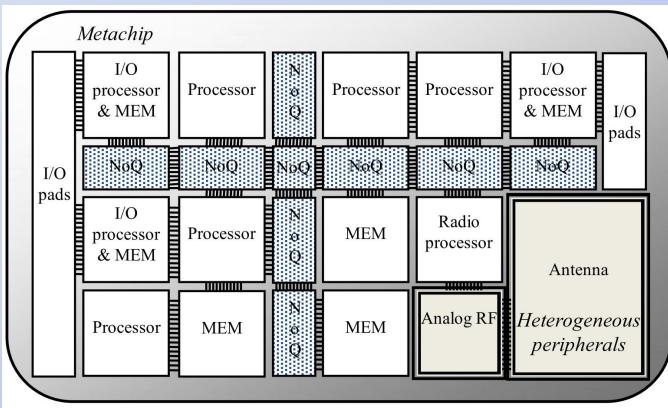

# **MPSoC** with Network Quilts

• General, heterogeneous multiprocessor system based on Network-on-Quilt (NoQ) tiles

32 Network on Metachip Architectures, NoCArc 2012, December 1st

Quilted Metachips, SoQs, NoQs

### CONCLUSION

33 Network on Metachip Architectures, NoCArc 2012, December 1st

# Summary of QP Features...

- Provides enormous bandwidth potential for analog and digital systems

- Direct-coupled millimeter-wave signals with extremely low loss

- Resonance-free, dc-coupled channel for digital signaling; no equalization needed

- Savings in decreased chip area offsets the additional fabrication costs – more die per wafer

- Also provides benefits for RF, networking extremely wide bandwidth, extremely low loss

# ...Summary of QP Features

- Quilt packaging is novel, unique and versatile

- Applications to new system architectures

- High speed, excellent signal integrity

- Smaller form factor, reduced weight

- Enables heterogeneous integration of dissimilar material systems, incompatible fabrication processes

- Extremely wide bandwidths with good signal integrity

- Intrinsic loss:

- < 0.1 dB from 50 MHz 100 GHz

- Bandwidth > 200 GHz from simulations

# Conclusions

Mapping SoC or NoC to the physical chips determines the IC fabrication economy

**Economy improves significantly via a metachip** Quilt nodule overhead << 1 % of silicon area

- Quilted architectures (SoQ, NoQ) enable efficient optimization and novel systems

- SoCs with faster and larger memory

- NoC with unprecedented size and complexity

- Heterogeneous integration