#### BREAKING MULTICAST DEADLOCK BY VIRTUAL CHANNEL ADDRESS/DATA FIFO DECOUPLING

Ka-Ming Keung, Akhilesh Tyagi

Iowa State University

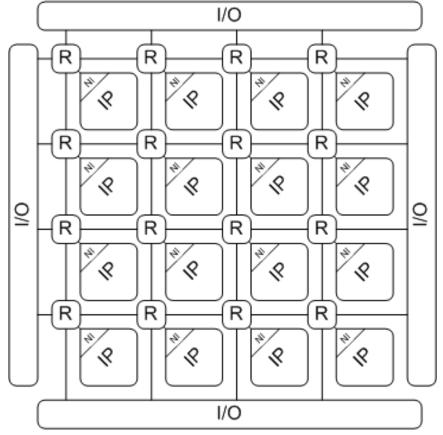

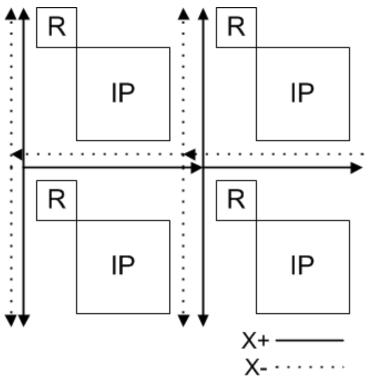

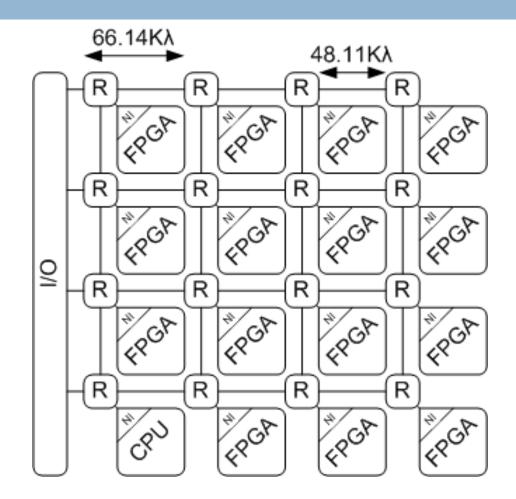

# On-Chip System with On-Chip Network

•Many tiles on a chip

•Communication among Tiles is supported by 2D Mesh Network

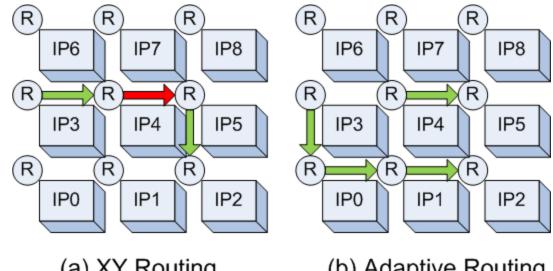

## Adaptive Routing

Allows packets being router through less congested channel.

(a) XY Routing

(b) Adaptive Routing

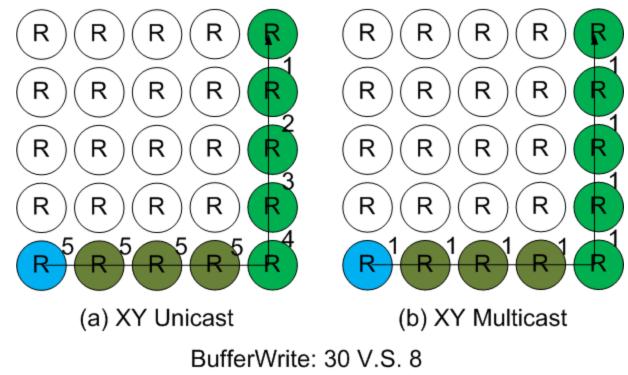

# Native Multicast Support

Avoid redundant unicast packets

- → Decrease Network Load

- → Reduce Packet Latency

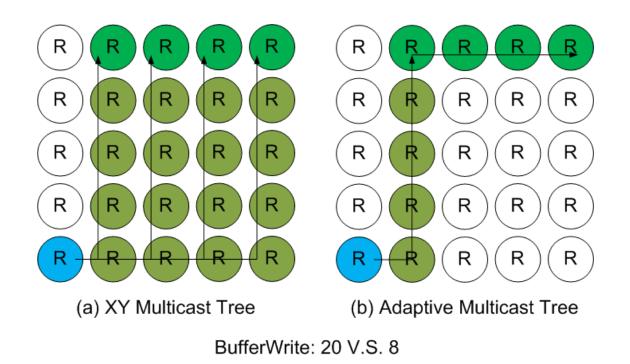

#### Adaptive Routing + Native Multicast Support

#### Allow dynamic multicast packet divergent points

→ Decrease Network Load

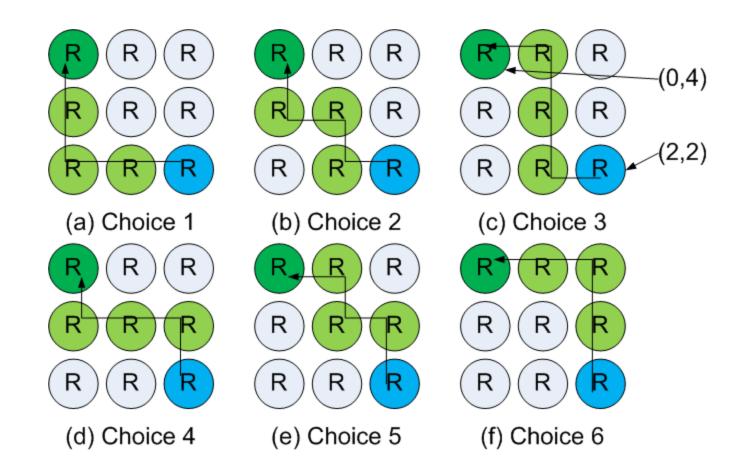

#### Path Based Adaptive Routing

#### Valid Path

| Choice | Route | Stop 0 | Stop 1 | Stop 2 | Stop 3 | OE<br>Viol | Valid |

|--------|-------|--------|--------|--------|--------|------------|-------|

| 1      | WWNN  | (2,2)  | (1,2)  | (0,2)  | (0,3)  | Free       | Yes   |

| 2      | WNWN  | (2,2)  | (1,2)  | (1,3)  | (0,3)  | Even       | No    |

| 3      | WNNW  | (2,2)  | (1,2)  | (1,3)  | (1,4)  | Even       | No    |

| 4      | NWWN  | (2,2)  | (2,3)  | (1,3)  | (0,3)  | Odd        | Yes   |

| 5      | NWNW  | (2,2)  | (2,3)  | (1,3)  | (1,4)  | Both       | No    |

| 6      | NNWW  | (2,2)  | (2,3)  | (2,4)  | (1,4)  | Odd        | Yes   |

Odd-Even Turn Model(Chiu et. al.) to ensure the network is deadlock free. Only route 1,4,6 are valid. Route 2,3,5 violate the odd-even routing rule

#### Path Based Adaptive Routing

#### Path Selection

- Channel Congestion(CC<sub>x,y,j</sub>) is measured by the total Channel Demand(CD<sub>x,y,i,j</sub>) by all router input buffers: CC<sub>x,y,j</sub>=CD<sub>x,y,north,j</sub>+CD<sub>x,y,east,j</sub>+CD<sub>x,y,west,j</sub>+ CD<sub>x,y,south,j</sub>+CD<sub>x,y,local,j</sub>

- Path Congestion (PC<sub>i</sub>) is the sum of the channel congestion along the path.  $PC_i = \sum CC_{x,y,j}$

Pick the valid path i with the lowest PC<sub>i</sub>

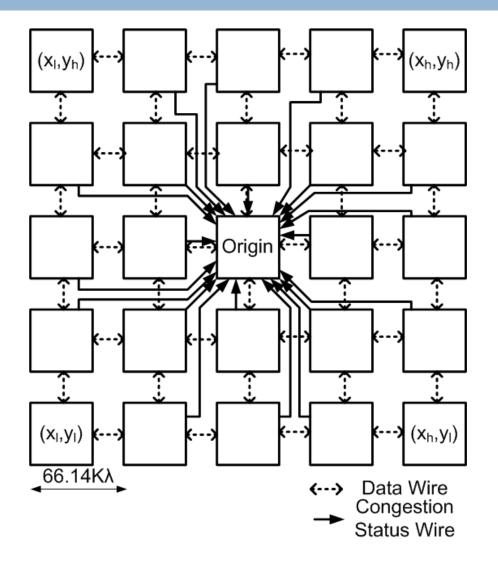

# **Observation Range**

- Intuition: Bigger observation range leads to better network performance.

- Bigger observation range requires

- More congestion status wires from the remote router

- Longer cost computation path

- → Potentially affects router clock frequency

- More adders and comparators

- → Higher Area Cost

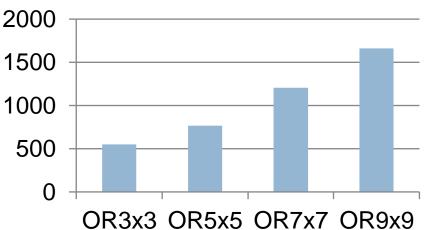

# **Observation Range**

Uniform Traffic Test:

- Low-Load Latency

- Stay the same

- Throughput

- 5x5 is 29% higher than 3x3

- 7x7 is 6% higher than 5x5

- 9x9 is 5.5% higher than 7x7

- RC Path

- 5x5 is 219ps longer than 3x3 2 1500

- 7x7 is 439ps longer than 5x5 %

- 9x9 is 453ps longer than 7x7

- We pick 5x5 to avoid RC stage becomes the critical stage

| Range        | Through | put(flits) | Latency(cycles) |        |  |

|--------------|---------|------------|-----------------|--------|--|

|              | vc9     | vc14       | vc9             | vc14   |  |

| $3 \times 3$ | 76444   | 103828     | 105.43          | 102.89 |  |

| $5 \times 5$ | 97541   | 133848     | 104.99          | 102.84 |  |

| $7 \times 7$ | 104081  | 142282     | 104.99          | 102.87 |  |

| $9 \times 9$ | 106842  | 150109     | 104.89          | 102.83 |  |

| XY           | 95529   | 118201     | 103.84          | 101.69 |  |

#### **Route Computation Path**

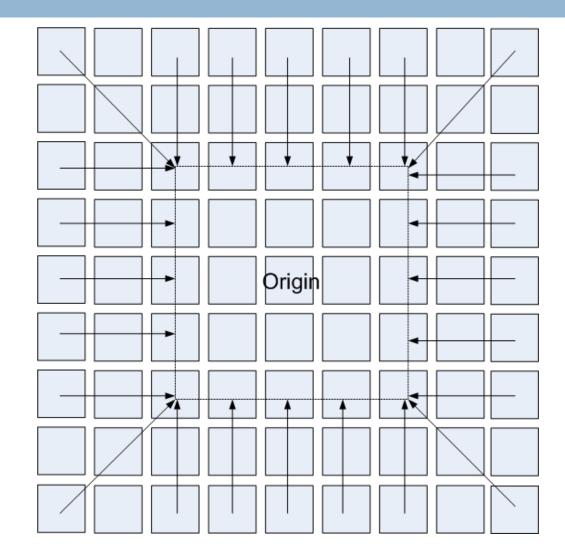

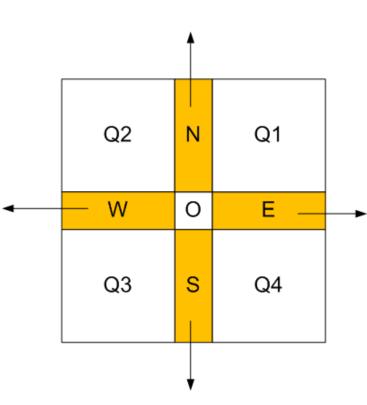

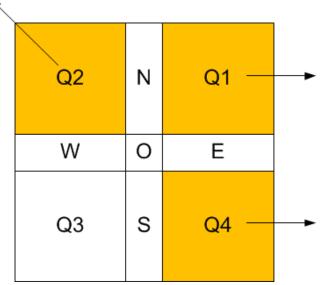

### Virtual Destinations

- Not all destination lies within the observation range

- For those destinations, we assume they lie on the observation range boundary

- Objective:

- Reduce the number of buffer write by diverging the packet as late as possible

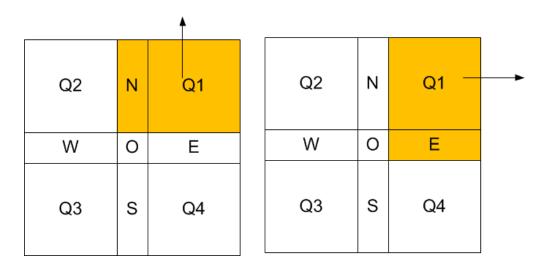

Rule 1(XY Destinations):

If the packet has directions in North, East, West and South, packet will be routed to the corresponding direction.

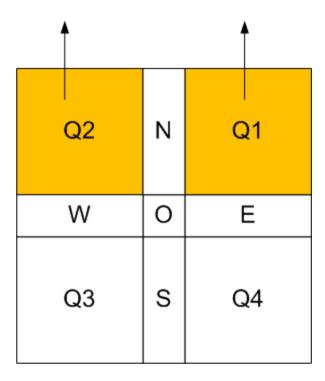

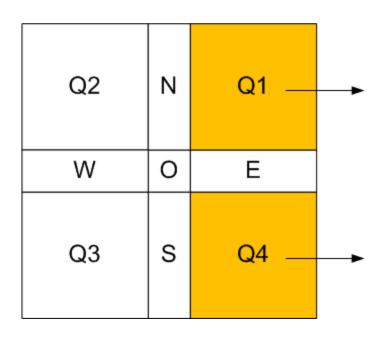

Rule 2 (Quadrant Destinations) :

In minimal routing, destinations at the quadrants can be routed horizontally(D<sub>h</sub>) or vertically(D<sub>v</sub>). If the packet has destination on either D<sub>h</sub> or D<sub>v</sub>, quadrant destinations will be routed to that direction.

Rule 3 (Quadrant Destinations):

Group the destinations which can't be routed by Rule 2 to a single routing direction.

Rule 4 (Quadrant Destinations):

Destinations which can't be routed by Rule 3 are routed using unicast adaptive routing to the virtual destination at the corner of the observation range.

| Q2 | N | Q1 |  |

|----|---|----|--|

| W  | 0 | E  |  |

| Q3 | S | Q4 |  |

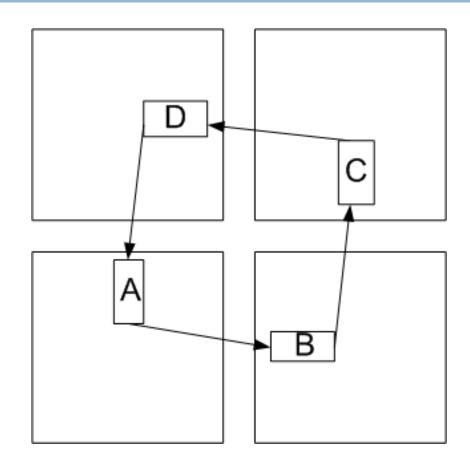

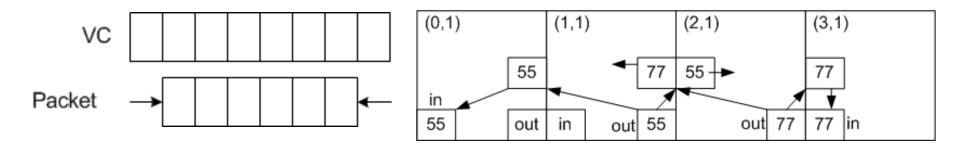

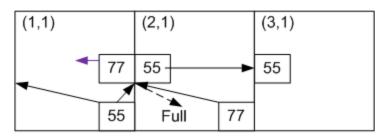

#### Unicast Deadlock

- Lock because of channel dependence

- XY-Routing is free from Unicast Deadlock

- Previous Solutions:

- 1. Ordered nodes and virtual channel (Dally et al.)

- 2. West-First, North-Last and Negative-first (Glass et al.)

- 3. Odd-Even Routing (Chiu)

- Lock because of channel dependence

- Even XY-Routing could suffer from Multicast Deadlock

- Example:

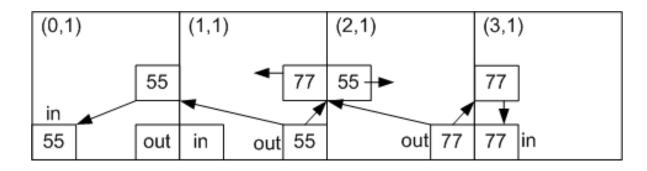

- Tile(1,1) sends multicast packet 55 to Tile (0,1), (3,1)

- Tile(2,1) sends multicast packet 77 to Tile(0,1), (3,1)

- Packet 55 does not release (0,1) E until it gets (3,1) W

- Packet 77 does not release (3,1) W until it gets (0,1) E

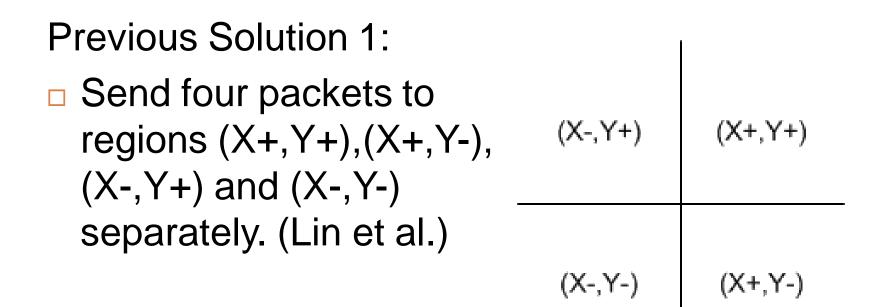

**Previous Solution 2:**

Hamiltonian Path

Pre-compute deadlock free path and store it in the packet header.

Routers route the packet following the stored path (Lin et al.)

Previous Solution 3:

Planar Network(Chien et al.)

Use two subnet networks X+ and X-.

X+ sub-network for packet with increasing X co-ordinate.

X- sub-network for packet with non-increasing X co-ordinate.

Simple Solution:

- Use Virtual Cut-through routing instead of wormhole routing.

- Router (0,1) East and (2,1) West can store the whole packet 55

- (0,1) East channel and (3,1) West channel are empty when the deadlock occurs.

- (1,1) out has no new flit for (0,1) East (Packet 55)

- □ (2,1) out has no new flit for (3,1) West (Packet 77)

- Deadlock is broken if packet 55 releases (0,1) East Channel and packet 77 releases (3,1) West channel

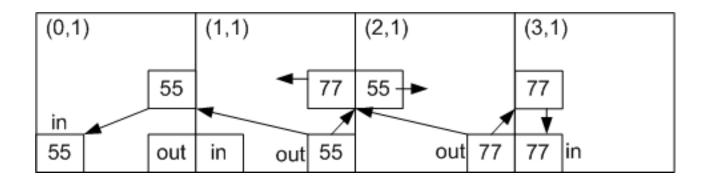

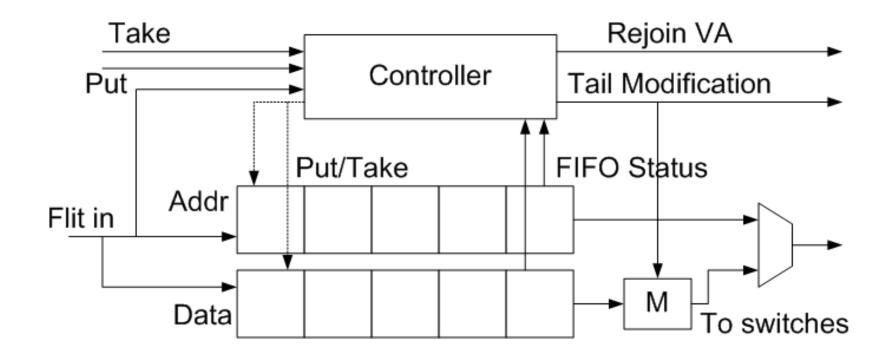

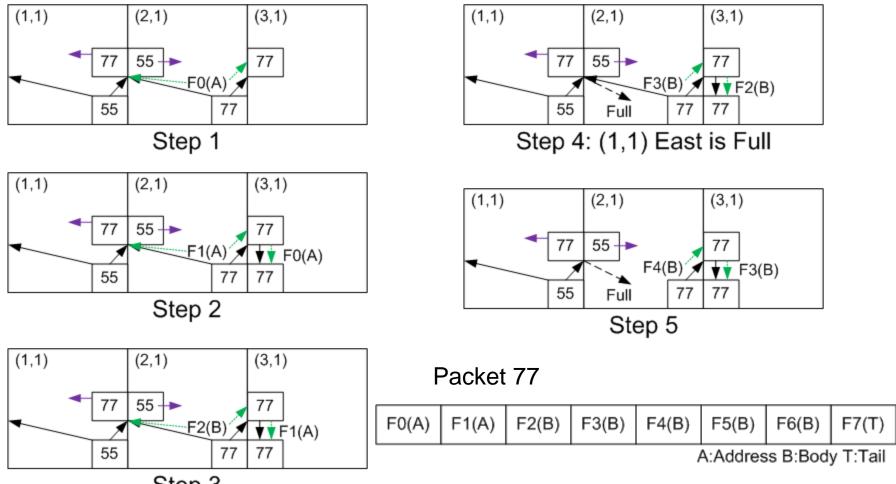

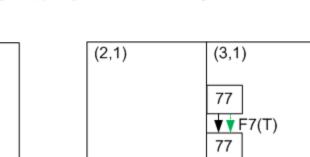

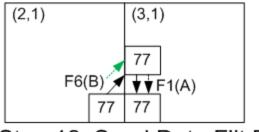

#### Address-Data FIFO Decoupling

Example: Each Virtual Channel can store 2 addr flits + 2 data flits

Step 3

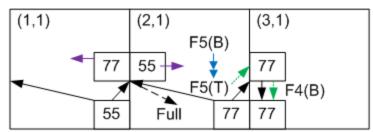

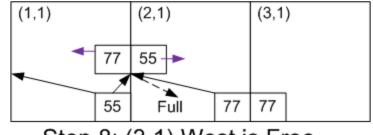

Example: Virtual Channel can store 2 addr flits + 2 data flits

Step 6: (2,1)out does not have F6 → Body to Tail Modification

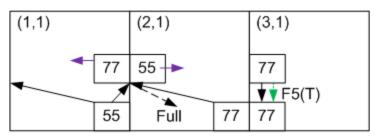

Step 8: (3,1) West is Free

Step 7 Packet 77 Releases (3,1) West

Step 9: Packet 55 obtains (3,1) West

Step 10: Resend Address Flit F0

(3,1)

77

F1(A)

77

**▼▼** F0(A)

(2,1)

Step 11: Resend Address Flit F1

Step 12: Send Data Flit F6

#### Packet 77 Received

Step 14

| F0(A) | F1(A) | F2(B) | F3(B) | F4(B)                 | F5(T) |  |  |

|-------|-------|-------|-------|-----------------------|-------|--|--|

| F0(A) | F1(A) | F6(B) | F7(T) | A:Address B:Body T:Ta |       |  |  |

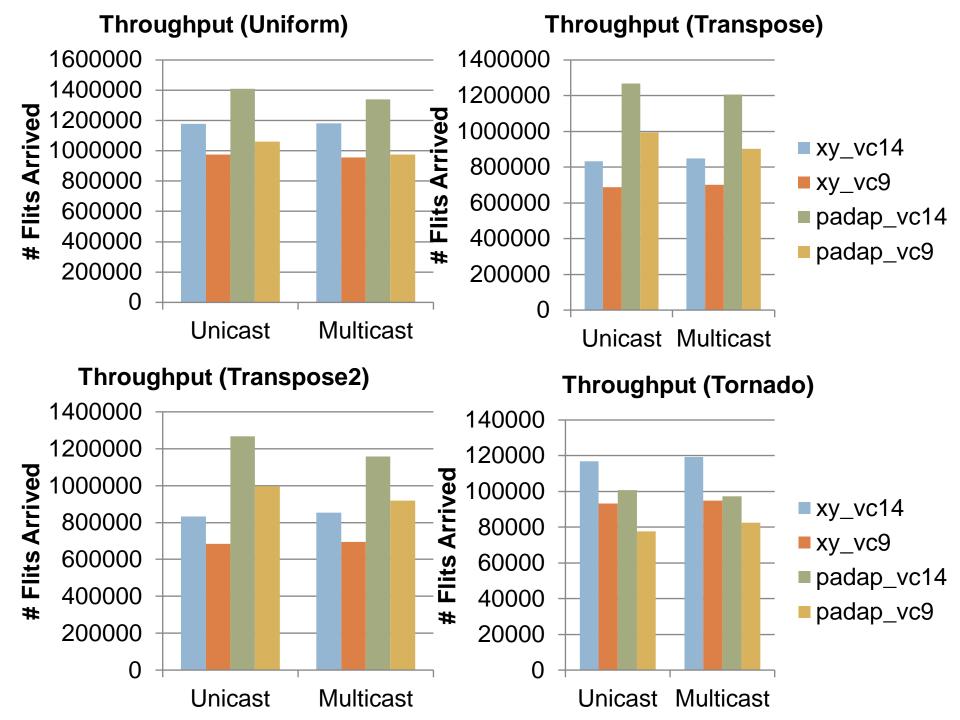

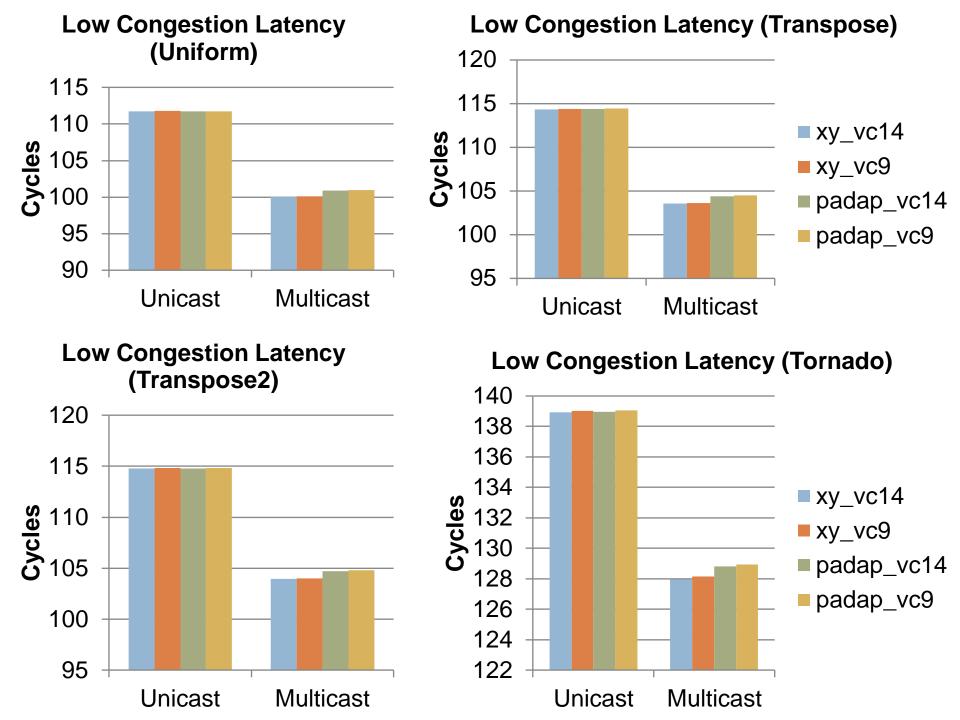

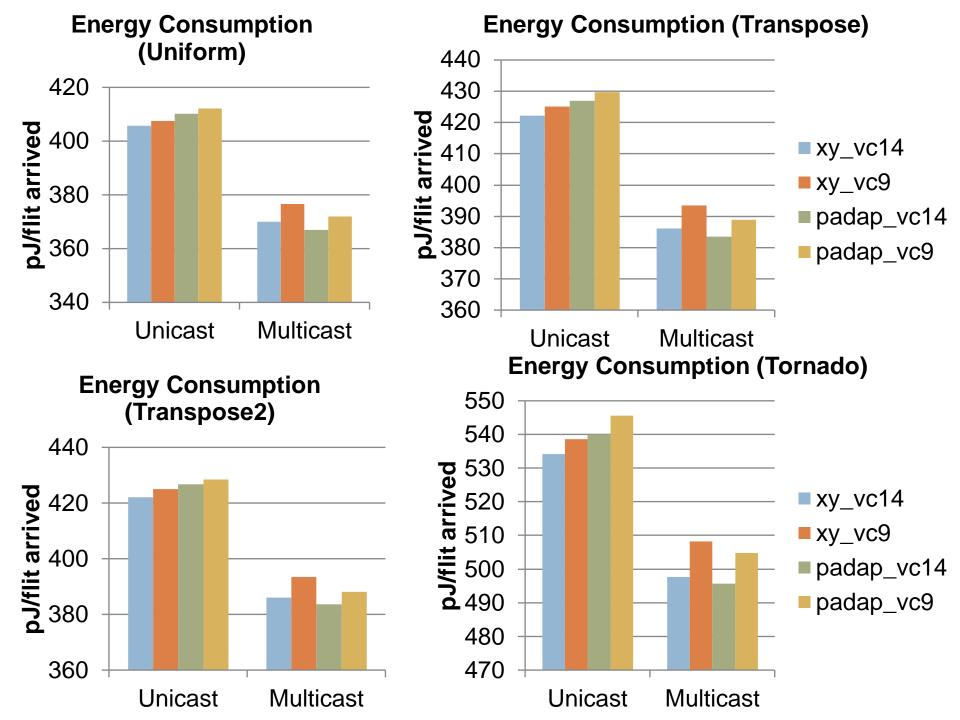

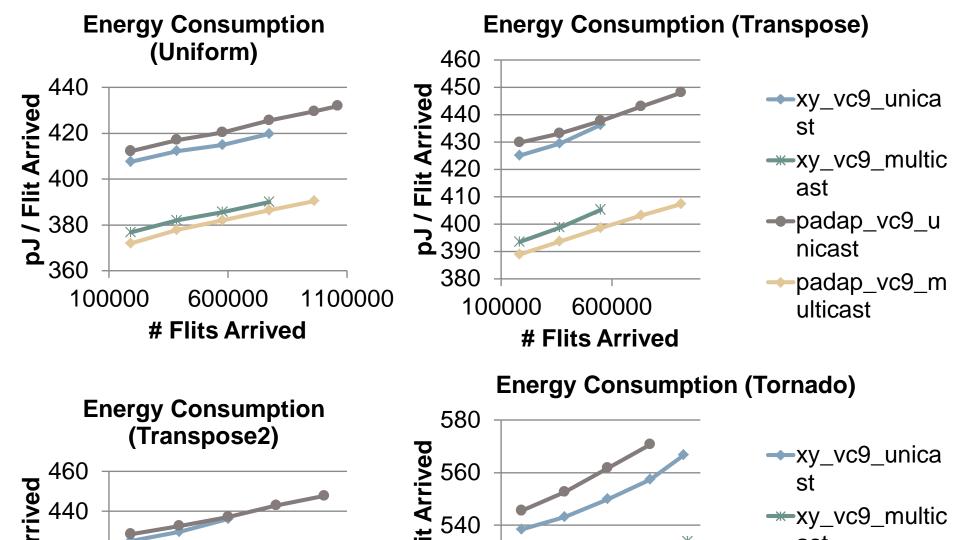

# Synthetic Traffic

- Four Types of synthetic traffics:

- Uniform Traffic

- Transpose Traffic (x,y)  $\rightarrow$  (N-1-y,N-1-x)

- Transpose2 Traffic  $(x,y) \rightarrow (y,x)$

- Tornado Traffic

- Multicast Group Size: 10

- Multicast Probability: 5%

# **Experimental Setup**

- Mesh Size: 20x20

- Flit Size: 128-bit

- Simulation Cycle: 30000

- Packet Length: 10 flits

- #Virtual Channel:

- 3 unicast channels (unicast router)

- 2 unicast + 1 multicast channel (multicast router)

- Virtual Channel Depth:

- 14 (Virtual Cut-Through)

- 9 (Address-Data FIFO decoupling)

xy\_vc9\_unica st

xy\_vc9\_multic ast

padap\_vc9\_u nicast

padap\_vc9\_m ulticast

# FPGA Traffic

- CPU controls the application jobs scheduling and placement

- Each tile contains its own configuration bitstream controller

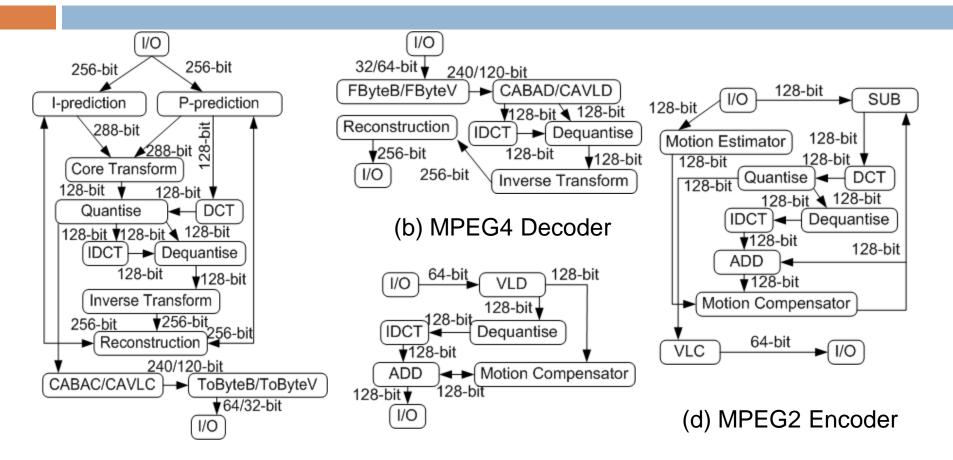

# Applications

(c) MPEG2 Decoder

(a) MPEG4 Encoder

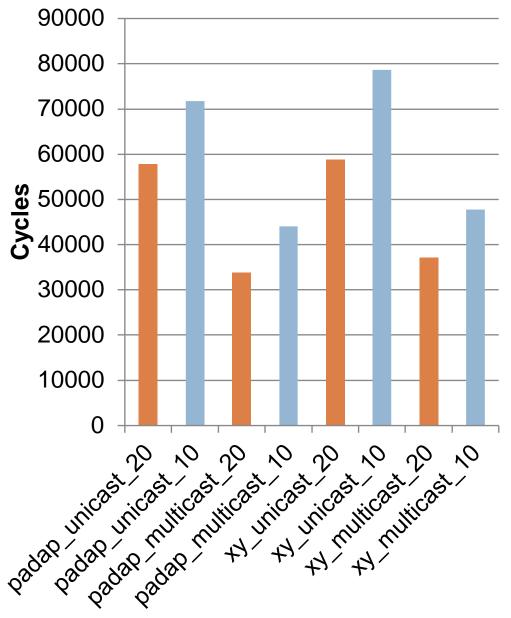

## **Experimental Setup**

- Mesh Size: 20x20

- Flit Size: 128-bit

- Simulation Cycle: 200,000,000

- Virtual Channel Depth: 14

- Max Packet Length:

- 10 (Virtual Cut-Through)

- 20 (Address-Data FIFO decoupling)

- #Virtual Channel:

- 3 unicast channels (unicast router)

- 2 unicast + 1 multicast channel (multicast router)

- Adaptive routing can reduce the configuration time by at most 10%

- With address-data decoupling, configuration time can be reduced by at most 25%

- Multicast support reduces configuration time by at most 40%

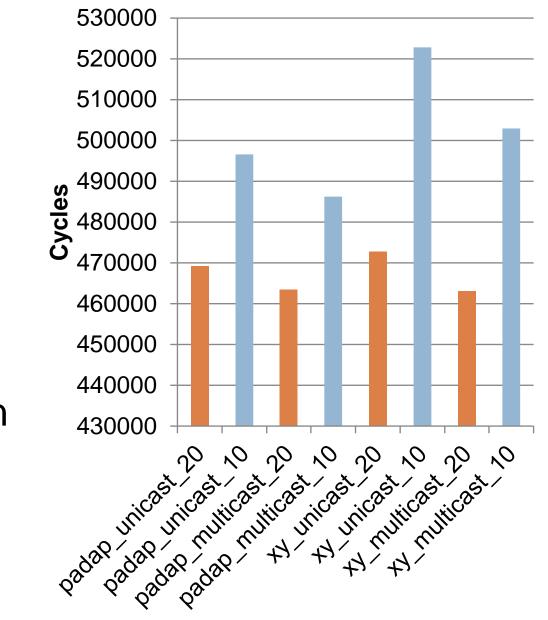

#### Average Tile Configuration Time

#### Average Application Runtime

- Adaptive routing can reduce the application runtime by at most 6%

- With address-data decoupling, application runtime can be reduced by at most 10%

- Multicast support reduces application runtime by at most 4%

- Adaptive routing can reduce the configuration energy by at most 4%

- With address-data decoupling, configuration energy can be reduced by at most 5%

- Multicast support reduces energy consumption by at most 20%

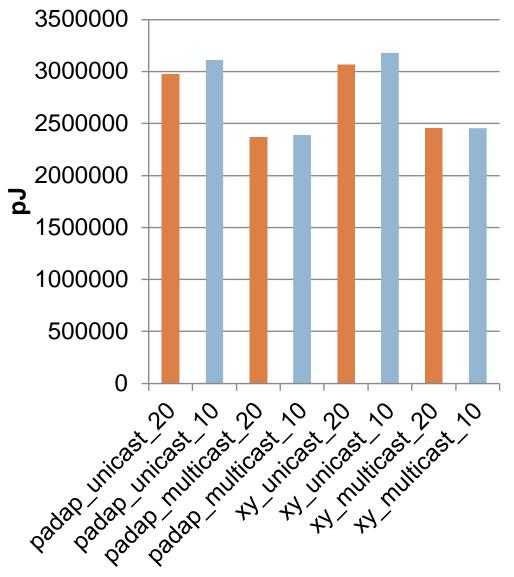

#### Network Energy Consumption per Tile Reconfiguration

#### Hardware Cost

| Router<br>type | XY/<br>Adaptive | Unicast/<br>Multicast | VC Depth | Area(Mλ <sup>2</sup> ) | RC(ps) | SA(ps) |

|----------------|-----------------|-----------------------|----------|------------------------|--------|--------|

| Wormhole       | XY              | Unicast               | 9        | 208                    | 375    | 1151   |

| Decouple       | XY              | Multicast             | 9        | 308                    | 528    | 1552   |

| VCT            | XY              | Multicast             | 14       | 396                    | 515    | 1161   |

| Wormhole       | Adaptive        | Unicast               | 9        | 216                    | 843    | 1125   |

| Decouple       | Adaptive        | Multicast             | 9        | 328                    | 1242   | 1616   |

| VCT            | Adaptive        | Multicast             | 14       | 417                    | 1197   | 1134   |

- With address-data decoupling, router can support packet with length 20 using 23% lesser area

- Address-data decoupling increases critical path by 35%

- Multicast support increases area by 50% in 2U+1M

#### This is the end of the presentation. Thank You.