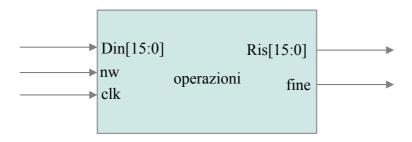

Il sistema ha il compito di realizzare una delle seguenti operazioni:

Not A codifica "00"

A+B codifica "01"

A-B codifica "10"

A+B[7:0]\*C[7:0] codifica "11"

Le operazioni da eseguire e gli operandi sono letti mediante l'ingresso Din. Nel primo ciclo di clock dopo l'attivazione dell'ingresso nw viene letta l'operazione da eseguire.

Sulla base del tipo di operazione viene letto un solo operando per la NOT, vengono letti due operandi per la somma e la differenza, tre operandi per l'ultima operazione.

Si assuma che gli operandi vengano letti uno alla volta e che sia richiesto un ciclo di clock per ogni lettura.

Non appena il segnale nw viene posto a '1' l'uscita fine viene posta a '0'. Al termine del calcolo il segnale fine viene posto a '1'.

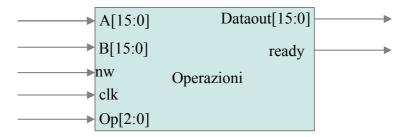

Questo sistema può realizzare una delle seguenti operazioni:

- Somma tra due numeri letti tramite gli ingressi A e B (Op="000")

- Differenza tra due numeri letti tramite gli ingressi A e B (Op="001")

- AND tra A e B (Op="010")

- OR tra A e B (Op="011")

- Prodotto tra A[7:0] e B[7:0] (Op="100").

Il prodotto è ottenuto sommando A per B volte ovvero

```

P=0;

conta=0;

while (conta < B)

{P=P+A;

conta++;}

```

Quando nw = '1' vengono letti sulle porte A,B e Op gli operandi e l'operazione da decodificare.

Dopo la decodifica, vengono eseguite le operazioni richieste.

Si supponga che tutte operazioni richiedano 1 solo ciclo di clock tranne il prodotto che richiede B cicli di clock.

Al termine dell'operazione il segnale ready viene posto a '1' per un ciclo di clock.

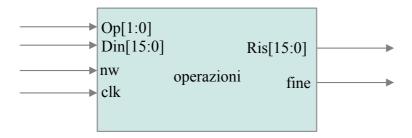

Il sistema ha il compito di realizzare una delle seguenti operazioni:

- Not A[15:0] codifica "00"

A[15:0]+B[15:0] codifica "01"

- A[15:0] OR B[15:0] codifica "10"

- A[15:8]\*A[7:0] codifica "11"

L'operazione da eseguire è letta mediante l'ingresso Op, gli operandi sono letti mediante l'ingresso Din.

Nel primo ciclo di clock dopo l'attivazione dell'ingresso nw viene letta l'operazione da eseguire e il primo operando.

Nel caso di somma o di OR, dopo avere letto il primo operando, viene letto nel ciclo di clock successivo il secondo operando.

Al termine della lettura degli operandi viene eseguita l'operazione.

Non appena il segnale nw viene posto a '1' l'uscita fine viene posta a '0'. Al termine del calcolo il segnale fine viene posto a '1'.

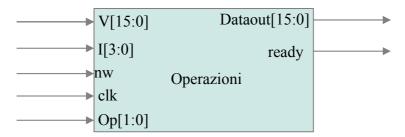

Il sistema ha al suo interno una memoria ROM di 16 locazioni da 1 byte e può realizzare una delle seguenti operazioni:

- Somma tra due numeri letti tramite l'ingresso V (V0+V1, Op="00")

- Somma tra un numero letto tramite l'ingresso V e un elemento della ROM di indice I (V + Mem(I) Op="01")

- Prodotto tra due numeri letti tramite l'ingresso V (V0[7:0] \* V1[7:0] Op="10").

- Prodotto tra un numero letto tramite l'ingresso V e un elemento della ROM di indice I (V [7:0]+ Mem(I) Op="11")

Quando nw = '1' vengono letti sulle porte V, Op e I, rispettivamente, il primo operando, l'operazione da decodificare e l'eventuale indice della memoria ROM. Dopo la decodifica, vengono eseguite le operazioni richieste.

Nel caso di somma o prodotto tra due operandi ( Op = "00" oppure Op="10"), dopo avere letto il primo operando, è necessario leggere un secondo operando nel successivo ciclo di clock.

Si supponga che la somma venga eseguita in un ciclo di clock e il prodotto in due cicli di clock.

Al termine dell'operazione il segnale ready viene posto a '1' per un ciclo di clock.