## **VLSI** Design Automation

## **IC** Products

- Processors

- CPU, DSP, Controllers

- Memory chips

- RAM, ROM, EEPROM

- Analog

- Mobile communication, audio/video processing

- Programmable

- PLA, FPGA

- Embedded systems

- Used in cars, factories

- Network cards

- System-on-chip (SoC)

## Integrated Circuit Revolution

1972: Intel 4004 Clock speed: 108 KHz # Transistors: 2,300 # I/O pins: 16 Technology: 10µm

2000: Intel Pentium 4 Clock speed: 1.5 GHz # Transistors: 42 million Technology: 0.18μm CMOS

2006: Intel Core 2 Duo Clock speed: 3.73 GHz # Transistors: 1 billion Technology: 65nm CMOS

## Integrated Circuit Revolution

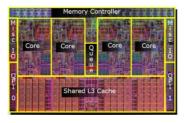

2009: Intel Core i7 Quadricore

3rd Generation Intel® Core™ Processor:

22nm Process

Core Core Core Core Graphics

Shared L3 Cache"

Memory Controller ID

Technology: 45nm CMOS

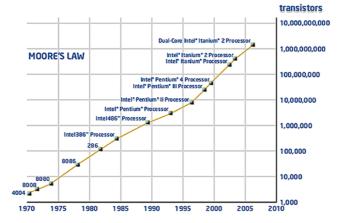

#### Moore's Law

Gordon Moore predicted in 1965 that the number of transistors that can be integrated on a die would double every 18 months.

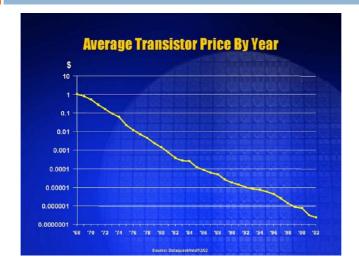

## Semiconductor Growth

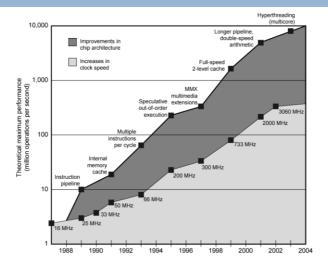

#### Intel Microprocessor Performance

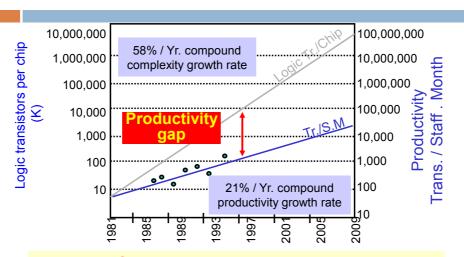

## **Device Complexity**

- Exponential increase in device complexity

- Increasing with Moore's law (or faster)!

- Require exponential increases in design productivity

We have exponentially more transistors!

## Stronger Market Pressures

- Time—to-market

- Decreasing design window

- Less tolerance for design revisions

## How Are We Doing?

Role of EDA: close the productivity gap

#### **Evolution of Design Methodology**

■ We are now entering the era of block-based design

# Yesterday Bus Standards, Predictable, Preverified

System-Board Integration

IP/Block Authoring

Today

VSI Compatible Standards,

Predictable, Preverified

System-Chip Integration

## What's Happening in SoCs?

■ Technology: no slow-down in sight!

Faster and smaller transistors:  $90 \rightarrow 65 \rightarrow 45 \rightarrow 32 \rightarrow 22$  nm

- → ... but slower wires, lower voltage, more noise!

- √ 80% or more of the delay of critical paths will be due to interconnects

- Design complexity: from 2 to 10 to 100 cores!

- → Design reuse is essential

- → ...but differentiation/innovation is key for winning on the market!

- Performance and power:

- → Performance requirements keep going up

- → ...but power budgets don't!

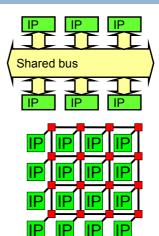

#### Communication Architectures

- Shared bus

- → Low area

- → Poor scalability

- → High energy consumption

- Network-on-Chip

- → Scalability and modularity

- → Low energy consumption

- → Increase of design complexity

## Intel's Teraflops

- 100 Million transistors

- 80 cores, 160 FP engines

- Teraflops perf. @ 62 Watts

- On-die mesh network

- Power aware design

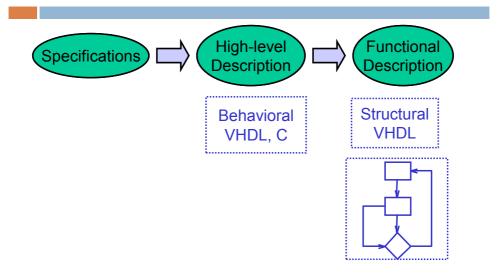

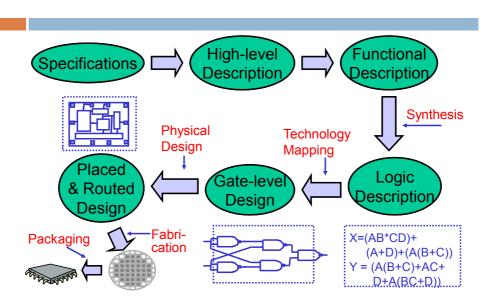

## IC Design Steps

## IC Design Steps

#### Circuit Models

- A model of a circuit is an abstraction

- A representation that shows relevant features without associated details

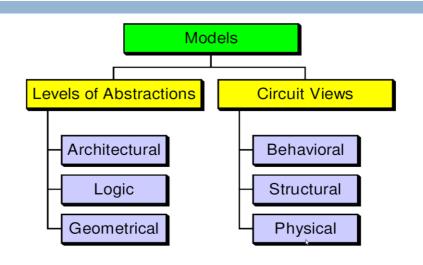

### **Model Classification**

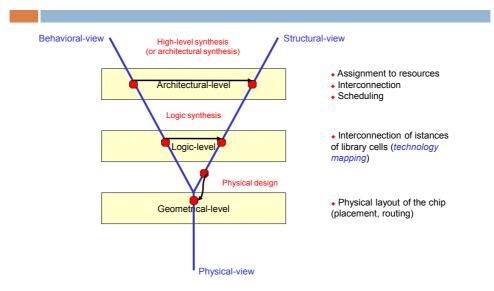

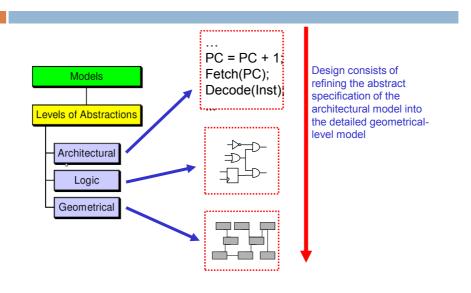

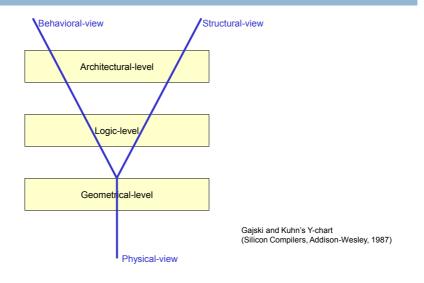

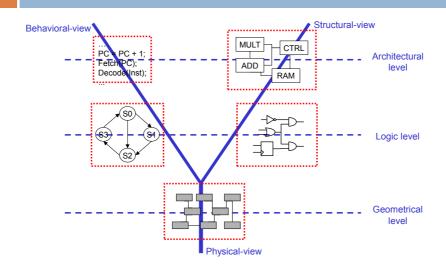

#### Levels of Abstraction

#### Architectural

- A circuit performs a set of operation, such as data computation or transfer

- √ HDL models, Flow diagrams, ...

#### Logic

- A circuit evaluate a set of logic functions

- √ FSMs, Schematics, ...

#### Geometrical

- A circuit is a set of geometrical entities

- ✓ Floor plans, layouts, ...

#### Levels of Abstraction

### Views of a Model

#### Behavioral

Describe the function of a circuit <u>regardless</u> of its implementation

#### Structural

Describe a model as an interconnection of components

#### Physical

- Relate to the physical object (e.g., transistors) of a design

### The Y-chart

### The Y-chart

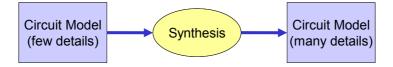

## Synthesis